Weet jij hoe je het EMI-probleem oplost bij meerlaags PCB-ontwerp?

Laat me je vertellen!

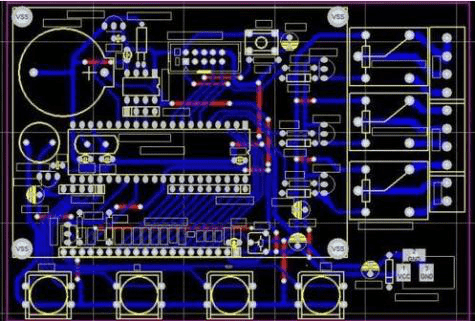

Er zijn veel manieren om EMI-problemen op te lossen.Moderne EMI-onderdrukkingsmethoden omvatten: het gebruik van EMI-onderdrukkingscoating, het selecteren van geschikte EMI-onderdrukkingsonderdelen en EMI-simulatieontwerp.Gebaseerd op de meest elementaire PCB-lay-out, bespreekt dit document de functie van PCB-stack bij het beheersen van EMI-straling en PCB-ontwerpvaardigheden.

stroom bus

De uitgangsspanningssprong van IC kan worden versneld door de juiste capaciteit in de buurt van de voedingspen van IC te plaatsen.Dit is echter niet het einde van het probleem.Vanwege de beperkte frequentierespons van de condensator is het voor de condensator onmogelijk om het harmonische vermogen te genereren dat nodig is om de IC-uitgang netjes in de volledige frequentieband aan te drijven.Bovendien zal de tijdelijke spanning die op de voedingsbus wordt gevormd een spanningsval veroorzaken aan beide uiteinden van de inductantie van het ontkoppelingspad.Deze tijdelijke spanningen zijn de belangrijkste EMI-storingsbronnen in de gemeenschappelijke modus.Hoe kunnen we deze problemen oplossen?

In het geval van IC op onze printplaat kan de vermogenslaag rond de IC worden beschouwd als een goede hoogfrequente condensator, die de energie kan verzamelen die is gelekt door de discrete condensator die hoogfrequente energie levert voor schone output.Bovendien is de inductantie van een goede vermogenslaag klein, dus het tijdelijke signaal dat door de inductor wordt gesynthetiseerd, is ook klein, waardoor de EMI in de gemeenschappelijke modus wordt verminderd.

Natuurlijk moet de verbinding tussen de voedingslaag en de IC-voedingspen zo kort mogelijk zijn, omdat de stijgende flank van het digitale signaal steeds sneller gaat.Het is beter om hem rechtstreeks aan te sluiten op de pad waar de IC-voedingspin zich bevindt, wat apart moet worden besproken.

Om EMI in de gewone modus te regelen, moet de vermogenslaag een goed ontworpen paar vermogenslagen zijn om te helpen ontkoppelen en een voldoende lage inductantie hebben.Sommige mensen zullen vragen, hoe goed is het?Het antwoord hangt af van de vermogenslaag, het materiaal tussen de lagen en de werkfrequentie (dwz een functie van IC-stijgtijd).Over het algemeen is de afstand tussen vermogenslagen 6 mil en is de tussenlaag FR4-materiaal, dus de equivalente capaciteit per vierkante inch vermogenslaag is ongeveer 75 pF.Het is duidelijk dat hoe kleiner de laagafstand, hoe groter de capaciteit.

Er zijn niet veel apparaten met een stijgtijd van 100-300ps, maar volgens de huidige ontwikkelingssnelheid van IC zullen de apparaten met een stijgtijd in het bereik van 100-300ps een groot deel innemen.Voor circuits met 100 tot 300 pk stijgtijden is een laagafstand van 3 mil niet langer van toepassing voor de meeste toepassingen.Op dat moment is het noodzakelijk om de delaminatietechnologie toe te passen met een tussenlaagafstand van minder dan 1 mil, en het FR4 diëlektrische materiaal te vervangen door het materiaal met een hoge diëlektrische constante.Nu kunnen keramiek en ingemaakte kunststoffen voldoen aan de ontwerpvereisten van 100 tot 300 ps stijgtijdcircuits.

Hoewel in de toekomst mogelijk nieuwe materialen en methoden zullen worden gebruikt, zijn gewone circuits met een stijgtijd van 1 tot 3 ns, een laagafstand van 3 tot 6 mil en diëlektrische FR4-materialen meestal voldoende om hoogwaardige harmonischen te verwerken en transiënte signalen laag genoeg te maken, dat wil zeggen , common-mode EMI kan zeer laag worden verlaagd.In dit artikel wordt het ontwerpvoorbeeld van PCB-gelaagde stapeling gegeven en wordt aangenomen dat de laagafstand 3 tot 6 mil is.

elektromagnetische afscherming

Vanuit het oogpunt van signaalroutering zou een goede laagstrategie moeten zijn om alle signaalsporen in een of meer lagen te plaatsen, die zich naast de vermogenslaag of het grondvlak bevinden.Voor stroomvoorziening zou een goede gelaagde strategie moeten zijn dat de vermogenslaag grenst aan het grondvlak en dat de afstand tussen de vermogenslaag en het grondvlak zo klein mogelijk moet zijn, wat we de "gelaagde" strategie noemen.

PCB-stapel

Welke stapelstrategie kan EMI helpen afschermen en onderdrukken?Het volgende gelaagde stapelschema gaat ervan uit dat de voedingsstroom op een enkele laag stroomt en dat een enkele spanning of meerdere spanningen worden verdeeld over verschillende delen van dezelfde laag.Het geval van meerdere machtslagen zal later worden besproken.

4-laags plaat

Er zijn enkele potentiële problemen bij het ontwerp van 4-laags laminaten.Allereerst, zelfs als de signaallaag zich in de buitenste laag bevindt en het vermogen en het grondvlak zich in de binnenste laag bevinden, is de afstand tussen de vermogenslaag en het grondvlak nog steeds te groot.

Als de kosteneis de eerste is, kunnen de volgende twee alternatieven voor de traditionele 4-laagse plaat worden overwogen.Beiden kunnen de EMI-onderdrukkingsprestaties verbeteren, maar ze zijn alleen geschikt voor het geval dat de dichtheid van de componenten op het bord laag genoeg is en er voldoende ruimte rond de componenten is (om de vereiste koperen coating voor de voeding te plaatsen).

Het eerste is het voorkeursschema.De buitenste lagen van de printplaat zijn allemaal lagen en de middelste twee lagen zijn signaal-/vermogenslagen.De voeding op de signaallaag wordt gerouteerd met brede lijnen, waardoor de padimpedantie van de voedingsstroom laag is en de impedantie van het pad van de microstrip van het signaal laag.Vanuit het perspectief van EMI-controle is dit de beste 4-laagse PCB-structuur die beschikbaar is.In het tweede schema draagt de buitenste laag de stroom en aarde, en de middelste twee lagen het signaal.Vergeleken met het traditionele 4-laags bord is de verbetering van dit schema kleiner en is de impedantie tussen de lagen niet zo goed als die van het traditionele 4-laags bord.

Als de bedradingsimpedantie moet worden gecontroleerd, moet het bovenstaande stapelschema heel voorzichtig zijn om de bedrading onder het koperen eiland van voeding en aarding te leggen.Bovendien moet het koperen eiland op de voeding of het stratum zoveel mogelijk onderling worden verbonden om de connectiviteit tussen DC en lage frequentie te waarborgen.

6-laags plaat

Als de dichtheid van de componenten op het 4-laags bord groot is, is de 6-laags plaat beter.Het afschermende effect van sommige stapelschema's in het ontwerp van een 6-laags bord is echter niet goed genoeg en het tijdelijke signaal van de voedingsbus wordt niet verminderd.Hieronder worden twee voorbeelden besproken.

In het eerste geval worden de voeding en aarde respectievelijk in de tweede en vijfde laag geplaatst.Vanwege de hoge impedantie van de met koper beklede voeding is het zeer ongunstig om de common mode EMI-straling te regelen.Vanuit het oogpunt van signaalimpedantieregeling is deze methode echter zeer correct.

In het tweede voorbeeld zijn de voeding en aarde respectievelijk in de derde en vierde laag geplaatst.Dit ontwerp lost het probleem van de met koper beklede impedantie van de voeding op.Vanwege de slechte elektromagnetische afschermingsprestaties van laag 1 en laag 6 neemt de EMI in differentiële modus toe.Als het aantal signaallijnen op de twee buitenste lagen het minst is en de lengte van de lijnen erg kort is (minder dan 1/20 van de hoogste harmonische golflengte van het signaal), kan het ontwerp het probleem van differentiële EMI-modus oplossen.De resultaten laten zien dat de onderdrukking van EMI in differentiële modus vooral goed is wanneer de buitenste laag is gevuld met koper en het met koper beklede gebied is geaard (elk 1/20 golflengte-interval).Zoals hierboven vermeld, zal koper worden gelegd

Posttijd: 29 juli 2020